Newsroom

PRESS RELEASES

July 18th, 2023

All-in-One Single Chip Architecture Meet Gen AI Challenges

VSORA today unveiled Jotunn™, an all-in-one single-chip family to provide a massive jump in performance for Generative AI inferencing processing challenges.

January 11th, 2023

VSORA Secures $4.2 Million in Financing from Otium Capital, Angel Investors

VSORA, an innovative startup offering silicon intellectual property (IP) solutions and autonomous driving/advanced driver assistance systems (AD/ADAS) compute platform chips for Level 2+ through Level 5 AD, today announced it closed a round of financing totaling $4.2 million.

January 12th, 2022

VSORA Introduces Tyr Chip Family Enabling L2-L5 Autonomous Driving

VSORA announced its first full silicon solution, called Tyr. Delivering between 258 Tflops and 1,032 Tflops and consuming as little as 10 Watts, Tyr allows users to implement autonomous driving functions previously not commercially viable.

October 6th, 2020

AD1028 - Petaflops L4/L5 Autonomous Driving Platform

VSORA announced a new powerful multi-Core DSP architecture that provides flexibility while eliminating any need for DSP co-processors, hardware accelerators or FPGAs.

February 14th, 2022

Leti, VSORA Show 5G NR Air Interface on Multi-Core DSP

Leti, a research institute of CEA Tech, and VSORA, which specializes in multi-core digital signal processor (DSP) design, today announced they have demonstrated the implementation of 5G New Radio (5G NR) Release 15 on a new DSP architecture that can dramatically reduce time to market of digital modems.

ARTICLES

March 11th, 2024

Meeting Challenges Posed by AI Inference at the Edge

GPU, the ubiquitous graphics processing unit, is arguably the most important computing technology today. It made AI processing possible but at an unsustainable cost, exacerbated by enormous power consumption.

January 2024

A solution to knock down the memory wall

As long as the escalating demand for powerful data processing outpaced the requirements for high bandwidth data movement, CPUs delivered what was expected from them. The rise of big data feeding high-performance computing (HPC) tilted the balance in favor of massive data movement throughput. A case in point is the elaboration of transformer algorithms in generative AI (GenAI) models that requires moving hundreds of billions of bytes every clock cycle, a daunting task that the CPU architecture cannot perform.

December 19th, 2023

11 Myths About Generative AI

Lauro Rizzatti breaks down the potential, deployment, and value of generative AI, along with misunderstandings and exaggerations to help debunk myths surrounding the technology.

November / December 2023

Why software is eating hardware

In 2011, venture capital investor Marc Andreessen wrote an opinion piece for The Wall Street Journal titled “Why Software Is Eating the World.” As part of this, he noted that it took 10 years after the wide adoption of the internet—and the dot-com economic bubble—for the new technology to bear fruit and suggested that this timeframe could be applicable to similar technological developments.

November 2nd, 2023

Parsing the Mindboggling Cost of Ownership of Generative AI

Current large language model (LLM) development focuses on creating smaller but more specialized LLMs that can run on existing hardware is a diversion. The GenAI industry needs semiconductor innovations in computing methods and architectures capable of delivering performance of multiple petaFLOPS with efficiency greater than 50%, reducing latency to less than two second per query, constraining energy consumption and shrinking cost to 0.2 cent per query.

October 10th, 2023

Long-standing Roadblock to Viable L4/L5 Autonomous Driving and Generative AI Inference at the Edge

Two recent software-based algorithmic technologies –– autonomous driving (ADAS/AD) and generative AI (GenAI) –– are keeping the semiconductor engineering community up at night. While ADAS at Level 2 and Level 3 are on track, AD at Levels 4 and 5 are far from reality, causing a drop in venture capital enthusiasm and money. Today, GenAI gets the attention, and VCs eagerly invest billions of dollars.

September 26th, 2023

System Challenges of Generative AI Inference Acceleration

When you look under the hood of generative AI processing, the system design challenges are many. Learn how efficiency, power consumption, and memory issues all come into play.

August 15th, 2023

Generative AI and memory wall: A wakeup call for IC industry

Judged by the presence of artificial intelligence (AI) and machine learning (ML) technologies at 2023 Design Automation Conference (DAC), the premiere event for semiconductor designers, computing hardware for accelerating AI/ML software workloads is finally receiving due attention. According to PitchBook Data, in the first six months of 2023, more than 100 startups designing novel AI/ML computing architectures collected $15.2 billion of venture funding.

July 25th, 2023

The Promise and Reality of Generative AI

Mass adoption of generative AI hinges on improving processing efficiency and lowering total cost of ownership. Similar to the internet and the invention of its World Wide Web application, generative AI has seized the public’s imagination. ChatGPT, the most popular AI chatbot launched a mere eight months ago, caught the world by surprise, reported to be the fastest growing app in history, reaching 100 million users within the first two months of its existence.

June 13th, 2023

Five Prerequisites for Realizing AD Vehicles

Five characteristics will underpin commercially viable autonomous-driving (AD) vehicle solutions at Levels 4 and 5: flexibility, high usable compute power, low latency, low power and low cost. The first three are mandatory to implement AD functionality. The last two, while not strictly necessary for meeting the target, are essential for achieving wide and rapid adoption. This article spotlights the technological attributes necessary to realize Level 4/5 autonomy.

January 18th, 2023

Vsora Unveils AI Chip Family to Enable L2–L5 Autonomous Driving

Paris-based digital-signal–processing (DSP) IP startup Vsora has introduced a family of PetaFLOPS computational companion chips to accelerate Level 3 (L3) through Level 5 (L5) autonomous-vehicle (AV) designs. Vsora has just raised $4.2 million in a pre-Series B round of financing to hasten its development.

September 1st, 2022

Look Ma, No Hands! The Road to Autonomous Driving

Remember that satisfying exclamation, "Look Ma, no hands!" when you were a child learning to ride a bicycle with no hands on the handlebars? Who wouldn't want to experience that feeling again, only this time behind the wheel of an automobile.

The article starts on page 9 of the magazine

August 25th, 2022

Implementation basics for autonomous driving vehicles

The automotive industry is delivering the first implementations of advanced driver-assistance systems (ADAS) for Level 2 (foot off the gas or break) and Level 3 (hands off the wheel) vehicles. Though it’s struggling to develop an autonomous driving (AD) system from L4 (eyes off the road) to L5 (completely self-driving and autonomous) vehicles. The challenge is turning out to be more difficult than anticipated a few years ago.

May 3rd, 2022

The Challenges to Achieve Level 4/Level 5 Autonomous Driving

The path to achieve fully autonomous driving (AD) progresses through five levels of increasing automation, as codified by the Society of Automobile Engineers (SAE) in 2014 under Standard J3016. It starts with L1 or basic driver assistance, and moves to L2, which means feet off the gas or break. L3, as in hands off the wheel, comes next, then L4 or eyes off the road to, finally, L5 that allows all passengers to have their minds off driving.

February 14th, 2022

VSORA Shifts Gears, Offers AI Chips

The Linley Group published this article in their "Microprocessor report". It is an extensive review of the Tyr1 compared to the Nvidia Orin and the Qualcomm AI 100. Conclusions are that the Tyr1 chip, which is built on the AD1028 architecture, provides 10x the performance of the Nvidia solution.

January 25th, 2021

The Linley Group 2020 Best Processor IP Award

VSORA announced it received The Linley Group’s Analysts’ Choice Award 2020 in the “Best Processor Intellectual Property (IP)” category for AD1028, the first PetaFLOPS computational platform to accelerate Level 4 (L4) and Level 5 (L5) autonomous vehicles designs.

December 7th, 2020

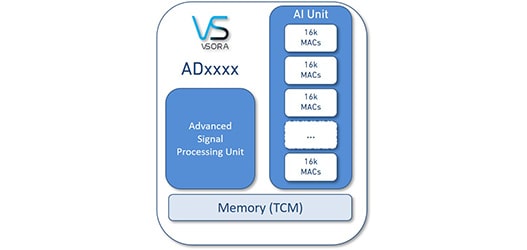

VSORA Drives to deliver Petaflops

VSORA has jumped into the race to provide DSPs and deep-learning accelerators (DLAs) for autonomous vehicles (AVs). The French startup aims to pass its more established rivals by offering the new ADxxxx intellectual property (IP), which it designed to handle perception and sensor fusion in Level 4 and 5 self-driving cars.

December 14th, 2020

Power Models For Machine Learning

Predicting the power or energy required to run an AI/ML algorithm is a complex task that requires accurate power models, none of which exist today. Power consumption spreads over a wide range, with worst-case scenarios sitting far away from typical consumption.

December 1st, 2020

VSORA Pushes the PetaFLOPS for Autonomous Driving

Autonomous driving is a wildly challenging problem. Of all the headline-grabbing technologies in development today, replacing the human driver in a car probably takes the most computing power, although you wouldn’t guess that from the obvious lack of computing power demonstrated by many of our fellow human drivers on the road.

August 4th, 2020

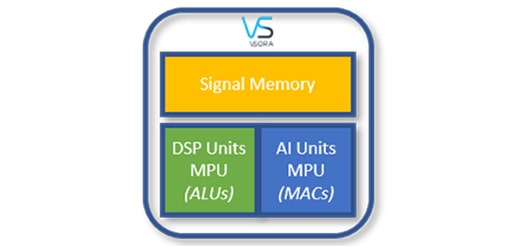

Combining AI And DSP On The Same Chip

VSORA devised a compact and efficient approach combining advanced digital signal processing (DSP) with AI algorithmic acceleration, on the same silicon, exchanging data via on-chip large memory, setting a new standard for performance, power consumption, efficiency, area and cost.

November 6th, 2018

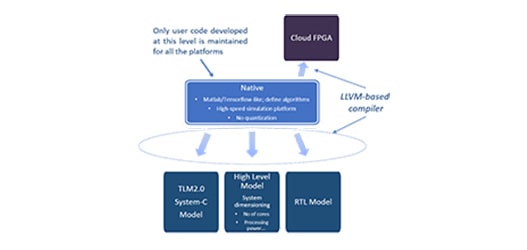

New DSP Approach to Accelerate 5G and AI Design

This article by Lauro Rizzatti discusses a more efficient flow to support DSP development groups, such as VSORA’s, could help to ensure the success of 5G.